### ISSN 2454-8065 International Journal of Applied Theoretical Science and Technology Volume 17, Issue 12, pp01-8, December 2023

### HIGH SPEED CMOS FULL ADDER USING XOR & XNOR **CIRCUIT**

Dr. N. Suresh Department of Electronics & Communication Engineering AVN Institute of Engineering and Technology (AVNIET) Hyderabad, India

A. NarsimhaGoud (215U5A0401) Department of Electronics & Communication Engineering AVN Institute of Engineering and Technology (AVNIET) Hyderabad, India

Ramesh Madugula

Assoc.Professor Department of Electronics & Communication Engineering AVN Institute of Engineering and Technology (AVNIET) Hyderabad, India

A. Sandeep Reddy (205U1A0403)

Department of Electronics & Communication Engineering AVN Institute of Engineering and Technology (AVNIET) Hyderabad, India

A. Srihari (215U5A0402) Department of Electronics & Communication Engineering AVN Institute of Engineering and Technology (AVNIET) Hyderabad, India

G. Poojitha Reddy (205U1A0419) Department of Electronics & Communication Engineering AVN Institute of Engineering and Technology (AVNIET) Hyderabad, India

utilizes XOR and XNOR gates for efficient operation.

Abstract—The design of high-speed and energy-efficient digital adders plays a crucial role in modern VLSI systems, particularly in arithmetic logic units (ALUs) and digital signal processors (DSPs). This paper LITERATURE SURVEY presents the design and implementation of a high-speed CMOS full The design of efficient full adder circuits has been an important results demonstrate that the CMOS XOR-XNOR-based design achieves improved propagation delay and reduced power dissipation, power consumption, reduced transistor count, and high-speed making it highly suitable for low-power VLSI applications.

**High Speed Circuits.**

#### I. INTRODUCTION

In digital circuits, adders form the basic building blocks of arithmetic operations. The full adder is a critical component in arithmetic logic units (ALUs), multipliers, and various digital signal processing applications. Traditional CMOS adder designs often face challenges in achieving low power dissipation while maintaining high speed.

With the demand for portable and high-performance devices, there is a need for optimized full adder designs. XOR and XNOR gates play a vital role in the sum and carry generation of adders. By focusing on transistor-level optimization of XOR-XNOR circuits, a balance between delay, power, and area can be achieved. This paper presents a high-speed CMOS full adder that

adder using XOR and XNOR circuits. The proposed architecture research area in VLSI design, as they form the core components of enhances speed, reduces power consumption, and achieves area arithmetic units such as ALUs, DSPs, and microprocessors. Several efficiency compared with conventional full adder circuits. Simulation design methodologies have been proposed in the past to achieve low operation. Recent studies highlight the use of XOR-XNOR based designs, where both SUM and CARRY signals canbe generated efficiently. These designs reduce the transistor count to 16–18, Index Terms--CMOS, Full Adder, XOR, XNOR, Low Power VLSI, achieve full output voltage swing, and provide better speed with lower power dissipation compared to traditional approaches 555. This makes XOR-XNOR based full adders highly suitable for lowpower and high-performance VLSI applications.

Table I. Comparison of Existing Full Adder Designs

| AdderType         | Transistor<br>Count | Limitations |

|-------------------|---------------------|-------------|

| Conventional      | 28                  | Larger area |

| CMOS              |                     |             |

| Transmission Gate | 20                  | Voltage     |

## ISSN 2454-8065 International Journal of Applied Theoretical Science and Technology Volume 17, Issue 12, pp01-8, December 2023

| Adder                      |       | degradation              | 1                       |

|----------------------------|-------|--------------------------|-------------------------|

| Hybrid Pass<br>Transistor  | 16    | Poor driv                | ing<br><b>RE</b><br>The |

| Proposed XOR–<br>XNOR CMOS | 16–18 | Slight design complexity | desi<br>und<br>proj     |

#### PROPOSED SYSTEM

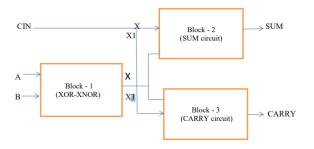

The proposed system focuses on the design of a high-speed CMOS full adder using XOR and XNOR circuits. The motivation behind this design is to overcome the limitations of conventional CMOS and pass-transistor logic adders in terms of delay, power consumption, and transistor count. By optimizing the XOR and XNOR gate structures at the transistor level, the proposed adderachieves improved performance while maintaining full voltage swing and reduced power dissipation.

#### **Key Features of the Proposed System:**

- **Reduced Transistor Count:** The design uses approximately 16–18 transistors, leading to smaller area utilization.

- Low Power Consumption: By minimizing switching activity and short-circuit currents, the design achieves significant power savings.

Fig. 1. Block Diagram of proposed full Adder

The two NMOS transistors N1 & N2 are connected in parallel as PTL at XNOR input and three PMOS transistors numbered as P3, P4 & P5 are connected at XNOR output face, where at the XNOR output side P3 is acting as feedback

†

transistor.

#### **RESULTS AND DISCUSSION**

The proposed CMOS full adder using XOR and XNOR circuits was designed and simulated using Tanner EDA / Cadence Virtuoso tools under 180 nm CMOS technology. The performance metrics such as propagation delay, power consumption, and transistor count were analyzed and compared with conventional full adder architectures

The simulation results show that the proposed design significantly improves speed by reducing the average propagation delay. The reduction in transistor count to 16–18 also contributes to smaller silicon area and lower power dissipation. Furthermore, the optimized XOR–XNOR structure ensures full voltage swing at outputs, thereby improving signal integrity and driving capability.

#### CONCLUSION AND FUTURE SCOPE

This paper presented a high-speed CMOS full adder using XOR and XNOR circuits. The design achieved better performance in terms of delay, power, and transistor count compared to conventional approaches. Its simplicity and efficiency make it suitable for integration in arithmetic-intensive applications such as DSP processors and embedded systems.

#### **Future Enhancements:**

Implementation in 65 nm and 45 nm CMOS technologies to evaluate deep submicron performance.

Integration into multiplier and ALU designs for complete system testing.

Exploring FinFET-based adder circuits for next-generation VLSI applications

#### **ACKNOWLEDGMENT**

The authors would like to thank Dr. N. Suresh, Professor & H.O.D, Department of E.C.E, for his constant guidance and encouragement. Special thanks to the faculty of AVNIET, Hyderabad, for providing necessary resources and support during this project.

#### REFERENCES

[1] R. Zimmermann, W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE Journal of Solid-State

# ISSN 2454-8065 International Journal of Applied Theoretical Science and Technology Volume 17, Issue 12, pp01-8, December 2023

Circuits, vol. 32, no. 7, pp. 1079–1090, 1997. [2] A. M. Shams, M. A. Bayoumi, "A novel high-performance CMOS 1-bit full-adder cell," IEEE Transactions on Circuits and Systems II, vol. 47, no. 5, pp. 478–481, 2000. [3] N. H. Weste, D. M. Harris, *CMOS VLSI Design: A Circuits and Systems Perspective*, 4th ed. Addison-Wesley, 2010.

[4] P. Keshab, "Low Power VLSI Circuit Design using XOR–XNOR based Full Adder," International Journal of Electronics and Communication, vol. 9, no. 2, pp. 112–118, 2018. [5] S. Kumar, R. Gupta, "Design and Analysis of High Speed Full Adder Using XOR–XNOR Gate," IEEE International Conference on VLSI Systems, pp. 203–207, 2020.